डीआईपी को समझें

डीआईपी एक प्लग-इन है। इस तरह से पैक किए गए चिप्स में पिन की दो पंक्तियाँ होती हैं, जिन्हें सीधे डीआईपी संरचना वाले चिप सॉकेट में वेल्ड किया जा सकता है या समान संख्या में छेदों वाले वेल्डिंग स्थानों पर वेल्ड किया जा सकता है। यह पीसीबी बोर्ड वेध वेल्डिंग के लिए बहुत सुविधाजनक है और मदरबोर्ड के साथ अच्छी संगतता रखता है, लेकिन इसकी पैकेजिंग क्षेत्र और मोटाई अपेक्षाकृत बड़ी होने के कारण, पिन डालने और निकालने की प्रक्रिया में आसानी से क्षतिग्रस्त हो जाते हैं, जिससे विश्वसनीयता कम होती है।

डीआईपी सबसे लोकप्रिय प्लग-इन पैकेज है, इसके अनुप्रयोग श्रेणी में मानक लॉजिक आईसी, मेमोरी एलएसआई, माइक्रो कंप्यूटर सर्किट आदि शामिल हैं। लघु प्रोफ़ाइल पैकेज (एसओपी), एसओजे (जे-प्रकार पिन लघु प्रोफ़ाइल पैकेज), टीएसओपी (पतला लघु प्रोफ़ाइल पैकेज), वीएसओपी (बहुत छोटा प्रोफ़ाइल पैकेज), एसएसओपी (कम एसओपी), टीएसएसओपी (पतला कम एसओपी) और एसओटी (लघु प्रोफ़ाइल ट्रांजिस्टर), एसओआईसी (लघु प्रोफ़ाइल एकीकृत सर्किट), आदि से व्युत्पन्न है।

डीआईपी डिवाइस असेंबली डिज़ाइन दोष

पीसीबी पैकेज का छेद डिवाइस से बड़ा है

पीसीबी प्लग-इन छेद और पैकेज पिन छेद विनिर्देशों के अनुसार बनाए जाते हैं। प्लेट बनाने के दौरान छेदों में तांबे की परत चढ़ाने की आवश्यकता के कारण, सामान्य सहनशीलता 0.075 मिमी से अधिक या कम होती है। यदि पीसीबी पैकेजिंग छेद भौतिक उपकरण के पिन से बहुत बड़ा है, तो इससे उपकरण ढीला हो जाएगा, टिन की कमी हो जाएगी, हवा में वेल्डिंग हो जाएगी और अन्य गुणवत्ता संबंधी समस्याएं हो सकती हैं।

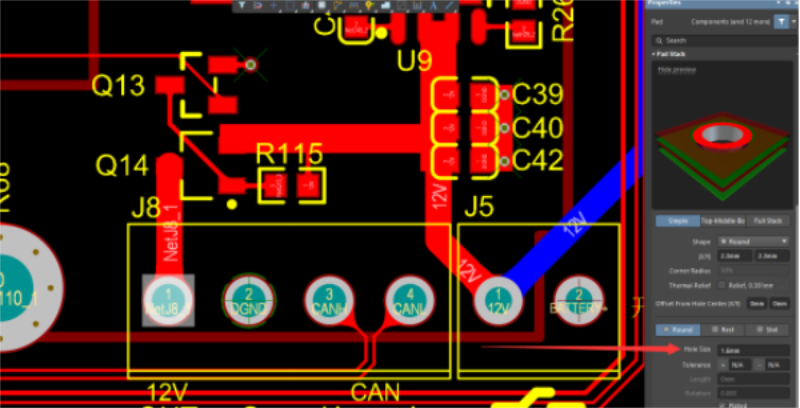

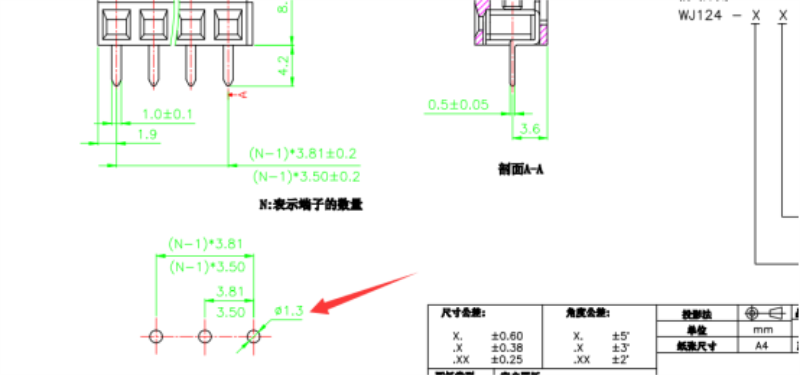

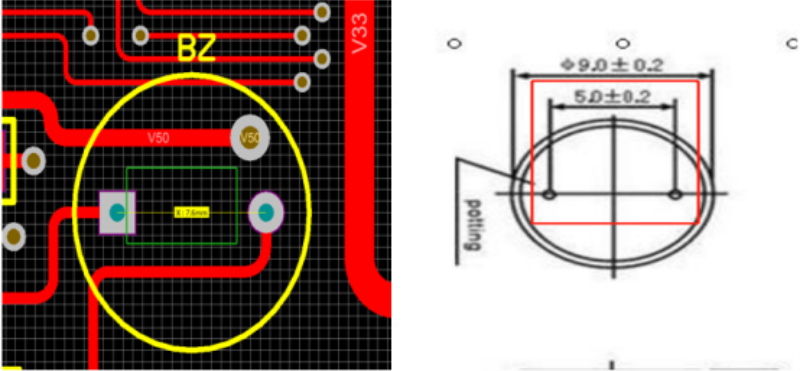

नीचे दिए गए चित्र को देखें, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) डिवाइस पिन का उपयोग 1.3 मिमी है, पीसीबी पैकेजिंग छेद 1.6 मिमी है, एपर्चर बहुत बड़ा है जिससे वेव वेल्डिंग स्पेस टाइम वेल्डिंग हो जाती है।

चित्र में संलग्न, डिज़ाइन आवश्यकताओं के अनुसार WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) घटक खरीदें, पिन 1.3 मिमी सही है।

पीसीबी पैकेज छेद डिवाइस से छोटा है

प्लग-इन, लेकिन कोई तांबा छेद नहीं होगा, अगर यह एकल और डबल पैनल है तो इस विधि का उपयोग कर सकते हैं, एकल और डबल पैनल बाहरी विद्युत चालन हैं, मिलाप प्रवाहकीय हो सकता है; मल्टीलेयर बोर्ड का प्लग-इन छेद छोटा है, और पीसीबी बोर्ड को केवल तभी बनाया जा सकता है जब आंतरिक परत में विद्युत चालन हो, क्योंकि आंतरिक परत चालन को रीमिंग द्वारा दूर नहीं किया जा सकता है।

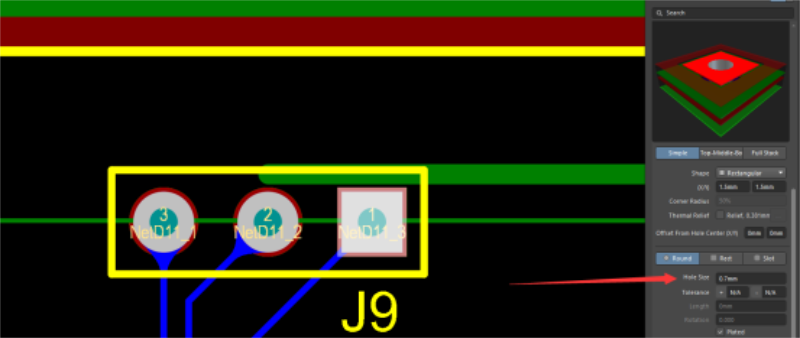

जैसा कि नीचे दिए गए चित्र में दिखाया गया है, A2541Hwv-3P_A2541HWV-3P (CJT) के घटक डिज़ाइन आवश्यकताओं के अनुसार खरीदे गए हैं। पिन 1.0 मिमी है, और PCB सीलिंग पैड छेद 0.7 मिमी है, जिसके परिणामस्वरूप सम्मिलन विफल हो रहा है।

A2541Hwv-3P_A2541HWV-3P (CJT) के घटक डिज़ाइन आवश्यकताओं के अनुसार खरीदे गए हैं। पिन 1.0 मिमी सही है।

पैकेज पिन स्पेसिंग डिवाइस स्पेसिंग से भिन्न होती है

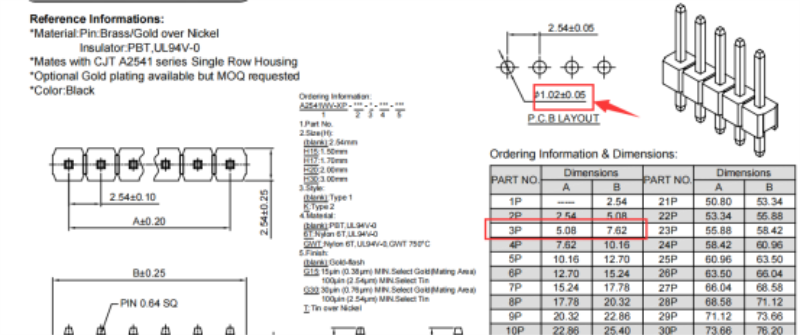

डीआईपी डिवाइस के पीसीबी सीलिंग पैड में न केवल पिन के समान एपर्चर होता है, बल्कि पिन होल के बीच भी समान दूरी की आवश्यकता होती है। यदि पिन होल और डिवाइस के बीच की दूरी असंगत है, तो डिवाइस को डाला नहीं जा सकता, सिवाय उन हिस्सों के जिनमें समायोज्य फ़ुट स्पेसिंग हो।

जैसा कि नीचे दिए गए चित्र में दिखाया गया है, पीसीबी पैकेजिंग के पिन होल की दूरी 7.6 मिमी है, और खरीदे गए घटकों के पिन होल की दूरी 5.0 मिमी है। 2.6 मिमी का अंतर डिवाइस को अनुपयोगी बना देता है।

पीसीबी पैकेजिंग छेद बहुत करीब हैं

पीसीबी डिज़ाइन, ड्राइंग और पैकेजिंग में, पिन होल के बीच की दूरी पर ध्यान देना ज़रूरी है। भले ही नंगी प्लेट उत्पन्न की जा सकती हो, पिन होल के बीच की दूरी छोटी होने पर, वेव सोल्डरिंग द्वारा असेंबली के दौरान टिन शॉर्ट सर्किट होने की संभावना अधिक होती है।

जैसा कि नीचे दिए गए चित्र में दिखाया गया है, शॉर्ट सर्किट पिन की छोटी दूरी के कारण हो सकता है। सोल्डरिंग टिन में शॉर्ट सर्किट होने के कई कारण होते हैं। यदि डिज़ाइन के स्तर पर ही संयोजनीयता को पहले से रोका जा सके, तो समस्याओं की संभावना कम हो सकती है।

डीआईपी डिवाइस पिन समस्या का मामला

समस्या विवरण

एक उत्पाद डीआईपी की वेव क्रेस्ट वेल्डिंग के बाद, यह पाया गया कि नेटवर्क सॉकेट के निश्चित पैर की सोल्डर प्लेट पर टिन की गंभीर कमी थी, जो एयर वेल्डिंग से संबंधित थी।

समस्या का प्रभाव

परिणामस्वरूप, नेटवर्क सॉकेट और पीसीबी बोर्ड की स्थिरता खराब हो जाती है, और उत्पाद के उपयोग के दौरान सिग्नल पिन पैर का बल लगाया जाएगा, जो अंततः सिग्नल पिन पैर के कनेक्शन को जन्म देगा, जिससे उत्पाद का प्रदर्शन प्रभावित होगा और उपयोगकर्ताओं के उपयोग में विफलता का जोखिम पैदा होगा।

समस्या विस्तार

नेटवर्क सॉकेट की स्थिरता खराब है, सिग्नल पिन का कनेक्शन प्रदर्शन खराब है, गुणवत्ता की समस्याएं हैं, इसलिए यह उपयोगकर्ता के लिए सुरक्षा जोखिम ला सकता है, अंतिम नुकसान अकल्पनीय है।

डीआईपी डिवाइस असेंबली विश्लेषण जांच

डीआईपी डिवाइस पिन से जुड़ी कई समस्याएं हैं, और कई महत्वपूर्ण बिंदुओं को आसानी से नज़रअंदाज़ किया जा सकता है, जिसके परिणामस्वरूप बोर्ड अंततः स्क्रैप हो जाता है। तो ऐसी समस्याओं का तुरंत और पूरी तरह से हमेशा के लिए समाधान कैसे किया जाए?

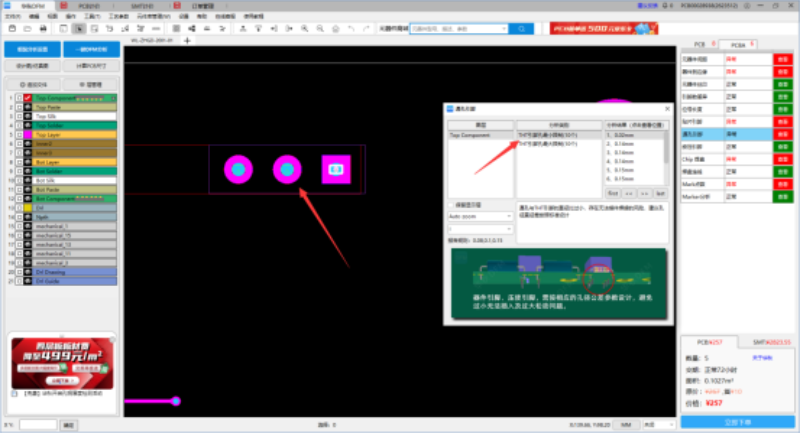

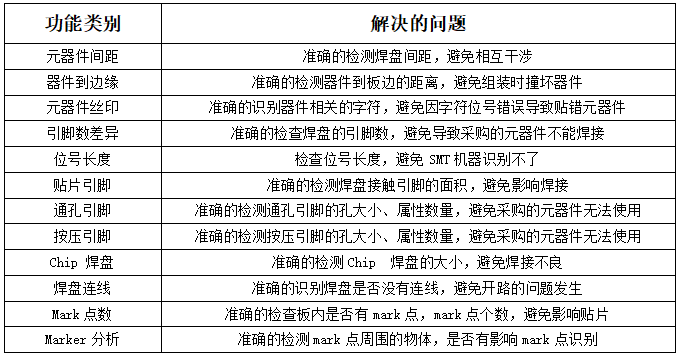

यहाँ, हमारे CHIPSTOCK.TOP सॉफ़्टवेयर के संयोजन और विश्लेषण फ़ंक्शन का उपयोग DIP उपकरणों के पिनों का विशेष निरीक्षण करने के लिए किया जा सकता है। निरीक्षण मदों में छिद्रों से गुजरने वाले पिनों की संख्या, THT पिनों की अधिकतम सीमा, THT पिनों की न्यूनतम सीमा और THT पिनों की विशेषताएँ शामिल हैं। पिनों के निरीक्षण मद मूलतः DIP उपकरणों के डिज़ाइन में संभावित समस्याओं को कवर करते हैं।

पीसीबी डिजाइन के पूरा होने के बाद, पीसीबीए असेंबली विश्लेषण फ़ंक्शन का उपयोग अग्रिम में डिज़ाइन दोषों की खोज करने, उत्पादन से पहले डिज़ाइन विसंगतियों को हल करने और असेंबली प्रक्रिया में डिज़ाइन समस्याओं से बचने, उत्पादन समय में देरी और अनुसंधान और विकास लागत को बर्बाद करने के लिए किया जा सकता है।

इसके असेंबली विश्लेषण फ़ंक्शन में 10 प्रमुख आइटम और 234 ठीक आइटम निरीक्षण नियम हैं, जो सभी संभावित असेंबली समस्याओं को कवर करते हैं, जैसे कि डिवाइस विश्लेषण, पिन विश्लेषण, पैड विश्लेषण, आदि, जो विभिन्न प्रकार की उत्पादन स्थितियों को हल कर सकते हैं जिन्हें इंजीनियर पहले से अनुमान नहीं लगा सकते हैं।

पोस्ट करने का समय: जुलाई-05-2023